T flip flop transistor schematic2/28/2024

T = 0 and present state = 1, then the next state = 1.T = 0 and present state = 0, then the next state = 0.When the T input is LOW, then the next sate of the T flip flop is same as the present state.

In simple terms, the operation of the T flip – flop is This will make the flip – flop to RESET i.e., Q = 0. This allows the Toggle Input to set the inputs for the RS Flip-Flop as R = 0 and S = 1. If the output Q = 1, then the upper NAND is in enable state and lower NAND gate is in disable condition. If you recall the truth table of RS Flip-Flop, this condition will SET the output. This means, the the Toggle Input will set the input condition for the RS Flip-Flop as R = 1 and S = 0. If the output Q = 0, then the upper NAND (NAND C) is in disable state (doesn’t have any dominating inputs) and lower NAND (NAND D) gate is in enable condition (feedback from Q is the dominating input). For example, consider a T flip – flop made of NAND SR latch as shown below.

The truth table of a T flip – flop is shown below.Īs mentioned earlier, T flip – flop is an edge triggered device. T flip – flop is an edge triggered device i.e., the low to high or high to low transitions on the input clock signal will cause a change in the output state of the flip – flop. The logic circuit of a T flip – flop constructed from a JK flip – flop is shown below. The J input and K input of the JK flip – flop are connected together and provided with the T input. The simplest of the constructions of a T flip – flop is with JK flip – flop. The circuit of a T flip – flop constructed from a D flip – flop is shown below. In D flip – flop, the output Q is XORed with the T input and given at the D input. Similarly, a T flip – flop can be constructed by modifying D flip – flop.

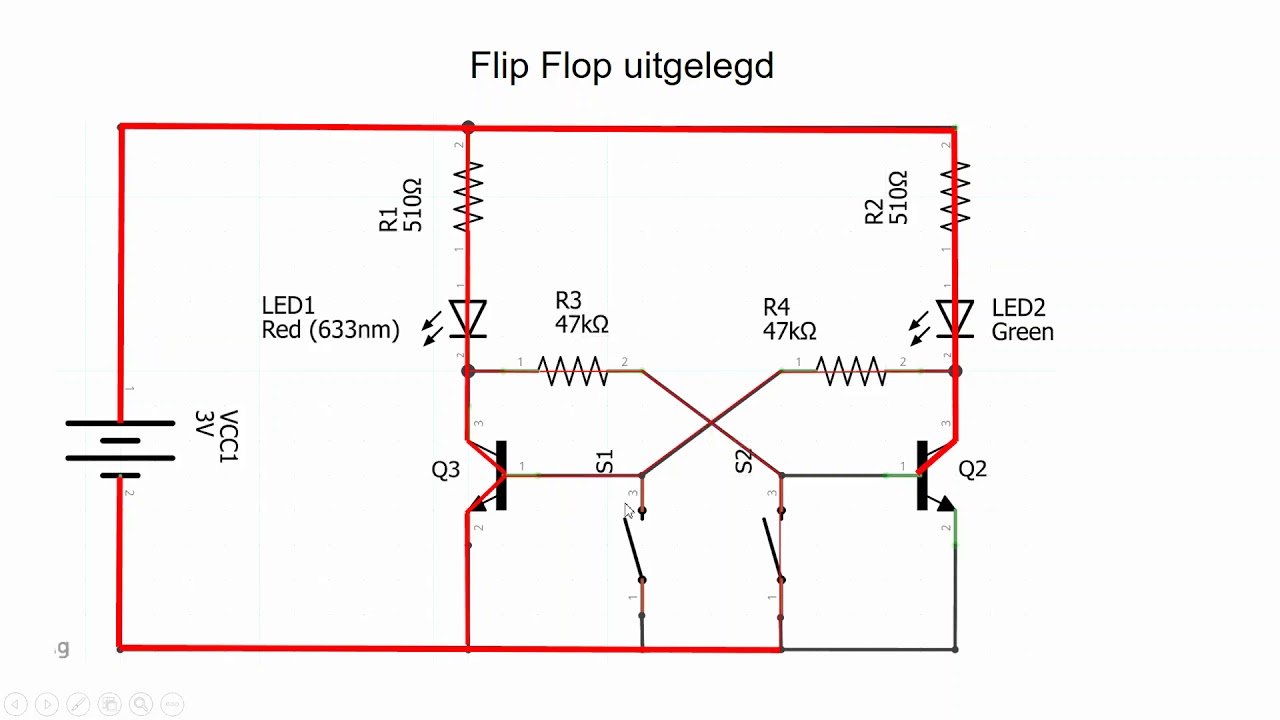

The circuit diagram of a T flip – flop constructed from SR latch is shown below. So, these flip – flops are also called Toggle flip – flops. In the T flip – flop, a pulse train of narrow triggers are provided as input (T) which will cause the change in output state of flip – flop. The AND gates are also connected with common Clock (CLK) signal. And one of the inputs to these AND gates are the feedback from the present state output Q and its complement Q to the respective AND gates i.e., Q to the AND Gate associated with R input and Q to the AND Gate associated with S input.Ī toggle input (T) is connected in common to both the AND gates as an input. We can construct a T flip – flop by connecting AND gates as input to the NOR gate SR latch. Hard – wiring the J and K inputs together and connecting it to T input in JK flip – flop.Connecting an XOR with T input and Q PREVIOUS output to the Data input in D flip – flop.Connecting the output feedback to the input in SR flip – flop.We can construct a T flip – flop by any of the following methods: It has one Toggle input (T) & one clock signal input (CLK). The logic symbol of T flip – flop is shown below. So, a T flip – flop is sometimes called as single input JK flip – flop. The T flip – flop is a single input device and hence by connecting J and K inputs together and giving them with single input called T, we can convert a JK flip – flop into T flip – flop. We can design the T flip – flop by making simple modifications to the JK flip – flop. Toggling means ‘Changing the next state output to complement of the present state output’. Then the flip – flop acts as a Toggle switch. To avoid the occurrence of intermediate state (also known as the forbidden state) in SR flip – flop, we should provide only one input to the flip – flop called the Trigger input or Toggle input (T). T flip – flop is also known as “Toggle Flip – flop”. 2-Bit Parallel Load Register using T flip – flops.

0 Comments

Leave a Reply.AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed